# T8302 Internet Protocol Telephone Advanced RISC Machine (*ARM*<sup>®</sup>) Ethernet QoS Using *IEEE*<sup>®</sup> 802.1q

# Description

The Agere Systems, Inc. Voice over Internet Protocol (VoIP) *Phone-On-A-Chip*<sup>™</sup> solution currently implements a quality of service (QoS) strategy that uses a proprietary voice packet prioritization scheme called Ethernet Quality of Service using BlackBurst (EQuB). This scheme uses an algorithm (implemented in **hardware**) to ensure that voice packets transmitted from the device are given the highest priority on their collision domain.

The *Phone-On-A-Chip* solution will now become more standards based by implementing a QoS strategy that incorporates a **software-based** *IEEE* 802.1q tagging protocol for outgoing Ethernet frames. This QoS implementation will utilize an *IEEE* 802.1q protocol stack from *Wind River Systems*<sup>®</sup> and will be integrated into the *VxWorks*<sup>®</sup> board support package (BSP) for the T8302 as part of our standard software solution. Virtual local area network (VLAN) tag insertion will be supported on a per-port, per-socket, and global basis.

**Note:** As a result of migrating to this software/standards-based priority scheme, Agere will no longer support its current proprietary hardware-based EQuB scheme.

Customers using the *Phone-On-A-Chip* IP Solution Development Design Kit should be aware of this enhancement and should structure their application software accordingly (to incorporate the features provided by the *IEEE* 802.1q stack).

It is hoped that this migration will aid customers of Agere in implementing their own systemwide QoS mechanism when designing their end product into an IP network.

Additional information may be obtained at the T8300 *Phone-On-A-Chip* website:

http://www.agere.com/phone\_chip

*ARM* is a registered trademark of Advanced RISC Machines Limited. *IEEE* is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc. *Wind River Systems* and *VxWorks* are registered trademarks of Wind River Systems, Inc.

For additional information, contact your Agere Systems Account Manager or the following: INTERNET: http://www.agere.com E-MAIL: docmaster@micro.lucent.com N. AMERICA: Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286 1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106) ASIA PACIFIC: Agere Systems Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256 Tel. (65) 778 8833, FAX (65) 777 7495 CHINA: Agere Systems (Shanghai) Co., Ltd., 33/F Jin Mao Tower, 88 Century Boulevard Pudong, Shanghai 200121 PRC Tel. (86) 21 50471212, FAX (86) 21 50472266 Agere Systems Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan JAPAN: Tel. (81) 3 5421 1600, FAX (81) 3 5421 1700 Data Requests: DATALINE: Tel. (44) 7000 582 368, FAX (44) 1189 328 148 EUROPE: Technical Inquiries: GERMANY: (49) 89 95086 0 (Munich), UNITED KINGDOM: (44) 1344 865 900 (Ascot), FRANCE: (33) 1 40 83 68 00 (Paris), SWEDEN: (46) 8 594 607 00 (Stockholm), FINLAND: (358) 9 3507670 (Helsinki), ITALY: (39) 02 6608131 (Milan), SPAIN: (34) 1 807 1441 (Madrid)

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. Phone-On-A-Chip is a trademark of Agere Systems, Inc.

Copyright © 2001 Agere Systems Inc. All Rights Reserved

# T8302 Internet Protocol Telephone Advanced RISC Machine (*ARM* \*)

# **1** Introduction

Agere Systems' Phone-On-A-Chip<sup>™</sup> IP Solution is a highly-integrated device set that forms the basic building blocks for an internet protocol telephone (IPT), residing on a local area network (LAN).

At this time, the IPT consists of two individual ICs, the T8302 IPT\_*ARM* (advanced RISC machine) and the companion T8301 IPT\_DSP (digital signal processor). This two-device solution comprises the basis for a single-IC integration of the system in the near future. The single-IC implementation will contain the functions of both IPT ICs.

For conceptual objectives, features for both ICs are listed in this document.

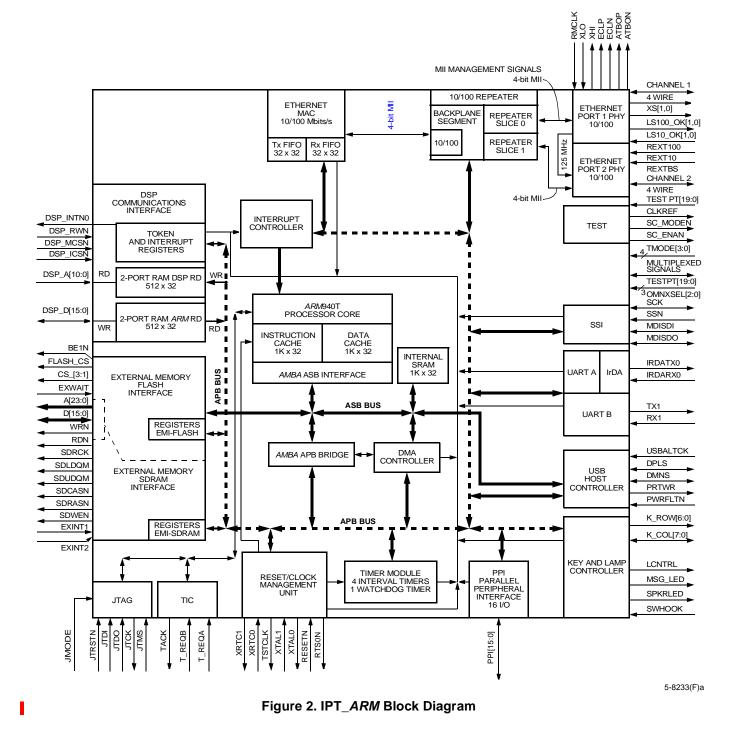

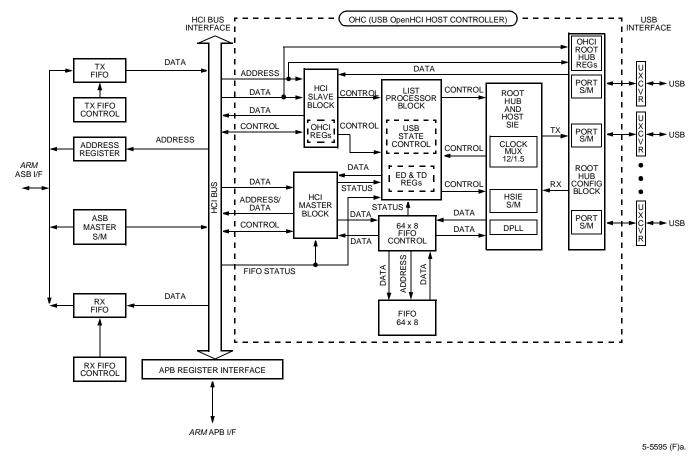

The general-purpose processor IC (IPT\_*ARM*) controls the system I/O (Ethernet, USB, IrDA, etc.) and provides general telephone control features (LED control, keypad button scanning, LCD module interface, etc.). A block diagram of the IPT\_*ARM* can be found in Figure 2 on page 27.

At the heart of the IPT\_DSP integrated circuit is Agere Systems' DSP1627 digital signal processor core. The DSP1627's high-performance (80 MIPS) and single-cycle multiply accumulate instruction provide excellent support for execution of voice compression/decompression and echo cancellation algorithms. The DSP1627 core and the digital-to-analog (D/A), analog-to-digital converters (A/D), low-pass filters, and audio amplifier circuitry drive standard business telephone handsets and speakerphone hardware.

This document describes the general-purpose processor IC T8302 for the IP phone. Throughout this discussion the IC will be referred to simply as IPT\_*ARM*.

\* ARM is a registered trademark of Advanced RISC Machines Limited.

# **Table of Contents**

# Contents

|   |                                                              | 4  |

|---|--------------------------------------------------------------|----|

| 1 |                                                              |    |

|   | 1.1 PT_ARM Features                                          |    |

| _ | 1.2 IPT_DSP Features                                         |    |

| 2 | Pinout Information                                           |    |

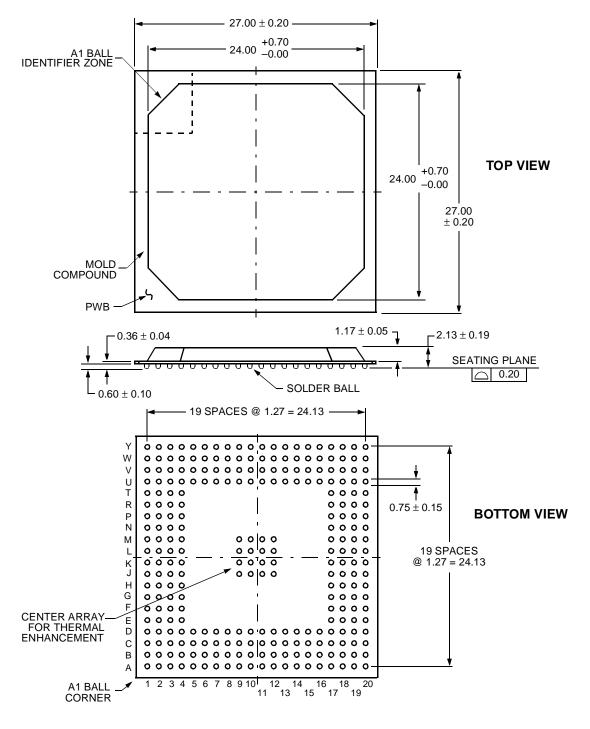

|   | 2.1 272-Pin PBGA Pin Diagram                                 |    |

| _ | 2.2 Pin List                                                 |    |

| 3 | Overview                                                     |    |

|   | 3.1 ARM 940T and AMBA Bridge                                 |    |

|   | 3.2 IPT_ARM Memory and I/O Map                               |    |

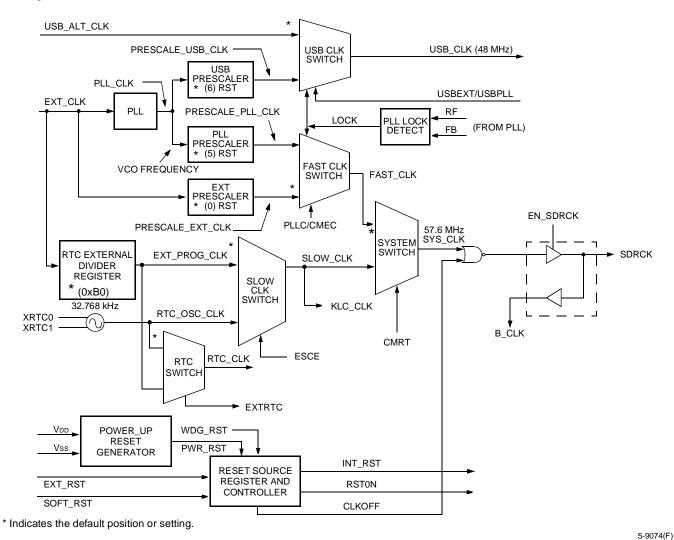

| 4 | Reset/Clock Management                                       |    |

|   | 4.1 Reset/Clock Management Controller Theory of Operation    |    |

|   | 4.1.1 Reset Operation                                        |    |

|   | 4.1.2 Operation of the Clock Switching Logic                 |    |

|   | 4.1.2.1 PLL Operation                                        |    |

|   | 4.1.3 Latency                                                | 33 |

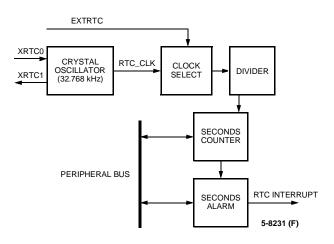

|   | 4.1.4 Real-Time Clock (RTC)                                  |    |

|   | 4.2 Reset/Clock Management Registers                         |    |

|   | 4.2.1 Pause Register                                         |    |

|   | 4.2.2 Version ID Register                                    |    |

|   | 4.2.3 Clock Management Register                              |    |

|   | 4.2.4 Clock Status Register                                  |    |

|   | 4.2.5 System Clock Source Encoding                           |    |

|   | 4.2.6 Clock Control Register                                 |    |

|   | 4.2.7 Soft Reset Register                                    |    |

|   | 4.2.8 PLL Control Register                                   |    |

|   | 4.2.9 Reset Status (Control/Clear) Registers                 |    |

|   | 4.2.10 Reset Peripheral Control (Read, Clear, Set) Registers |    |

|   | 4.2.11 RTC External Divider Register                         |    |

|   | 4.2.12 RTC Clock Prescale Registers                          |    |

|   | 4.2.12 RTC Control Register                                  |    |

|   | 4.2.13 RTC Control Register                                  |    |

|   | 4.2.15 RTC Seconds Count Register                            |    |

|   |                                                              |    |

|   | 4.2.16 RTC Divider Register                                  |    |

|   | 4.2.17 RTC Interrupt Status Register                         |    |

|   | 4.2.18 RTC Interrupt Enable Register                         |    |

| ~ | 4.3 Operation on Reset                                       |    |

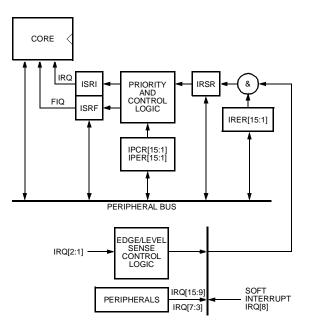

| 5 | Programmable Interrupt Controller (PIC)                      |    |

|   | 5.1 Interrupt Controller Operation                           |    |

|   | 5.1.1 Interrupt Registers                                    |    |

|   | 5.2 Programmable Interrupt Controller Registers              |    |

|   | 5.2.1 Interrupt Request Status Register IRSR                 |    |

|   | 5.2.2 Interrupt Request Enable Registers IRER (Set, Clear)   |    |

|   | 5.2.3 Interrupt Request Soft Register IRQSR                  |    |

|   | 5.2.4 Interrupt Priority Control Registers IPCR[15:1]        |    |

|   | 5.2.5 Interrupt In-Service Registers ISR (ISRI, ISRF)        |    |

|   | 5.2.6 Interrupt Request Source Clear Register IRQESCR        |    |

|   | 5.2.7 Interrupt Priority Enable Registers IPER (Set, Clear)  |    |

|   | 5.2.8 External Interrupt Control Registers                   |    |

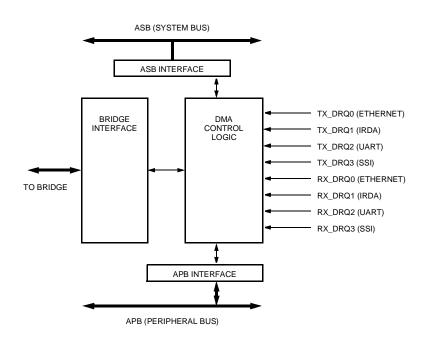

| 6 | Programmable Direct Memory Access (DMA) Controller           | 56 |

|   | 6.1 DMA Operation                                            | 56 |

Page

2

# Contents

|   | 6.1.1 DMA Transfer Setup Procedure                                                      |    |

|---|-----------------------------------------------------------------------------------------|----|

|   | 6.1.2 DMA Mode 0. Memory-to-Memory in Blocks of Burst Count Size                        |    |

|   | 6.1.3 Mode 1. Peripheral-to-Memory in Blocks of Burst Count Size                        |    |

|   | 6.1.4 Mode 2. Memory-to-Peripheral in Blocks of Burst Count Size                        | 59 |

|   | 6.1.4.1 Software-Triggered DMA Mode                                                     | 60 |

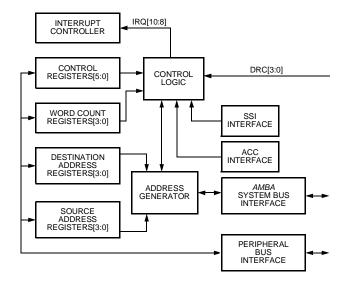

|   | 6.2 DMA Registers                                                                       | 61 |

|   | 6.2.1 DMA Control Registers for Channels [0:3]                                          | 62 |

|   | 6.2.2 DMA Source Address Registers for Channels [0:3]                                   | 63 |

|   | 6.2.3 DMA Preload Destination Start Address Registers for Channels [0:3]                | 64 |

|   | 6.2.4 DMA Preload Transfer Count Registers for Channels [0:3]                           |    |

|   | 6.2.5 DMA Transfer Count Registers for Channels [0:3]                                   |    |

|   | 6.2.6 DMA Burst and Hold Count Registers                                                |    |

|   | 6.2.7 DMA Status Register                                                               | 66 |

|   | 6.2.8 DMA Interrupt Register                                                            |    |

|   | 6.2.9 DMA Interrupt Enable Register                                                     | 68 |

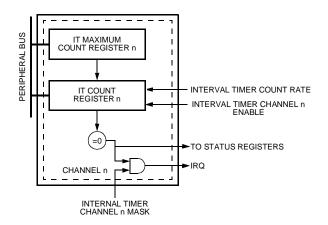

| 7 | Programmable Timers                                                                     |    |

|   | 7.1 Timers Operation                                                                    | 70 |

|   | 7.2 Interval Timer (IT)                                                                 | 70 |

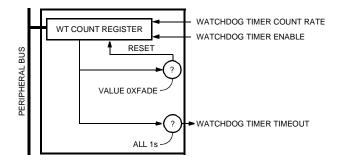

|   | 7.3 Watchdog Timer                                                                      | 71 |

|   | 7.4 Timer Registers                                                                     | 73 |

|   | 7.4.1 Count Rate Register                                                               |    |

|   | 7.4.2 Encoding of Interval Timer Count Rates (ITR) and Watchdog Timer Count Rates (WTR) |    |

|   | 7.4.3 WT Timer Count Register                                                           |    |

|   | 7.4.4 Timer Status Register                                                             |    |

|   | 7.4.5 Timer Interrupt Mask Register                                                     |    |

|   | 7.4.6 Timer Control Register                                                            |    |

|   | 7.4.7 IT Count Registers                                                                |    |

| 8 | External Memory Interface (EMI)                                                         |    |

|   | 8.1 IPT_ARM Processor Memory Map                                                        |    |

|   | 8.2 External FLASH/SRAM Memory Interface (EMI FLASH)                                    | 78 |

|   | 8.3 EMI FLASH Memory Access                                                             |    |

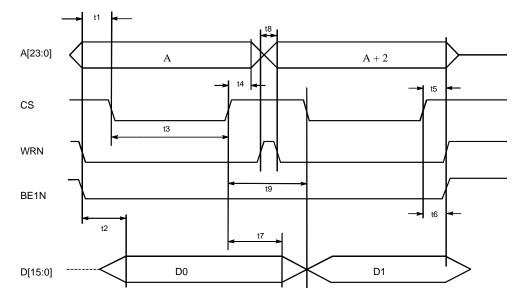

|   | 8.3.1 External Write                                                                    |    |

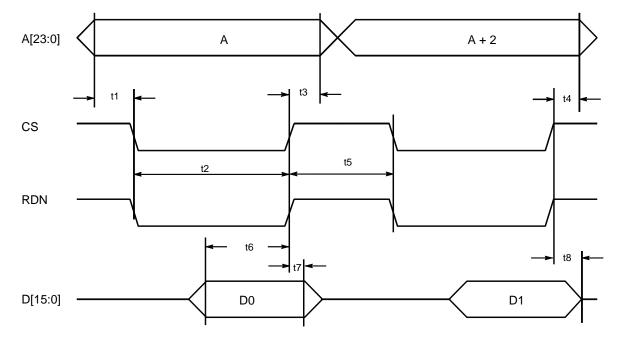

|   | 8.3.2 External Read                                                                     |    |

|   | 8.3.3 Wait-States                                                                       |    |

|   | 8.3.4 Hold State                                                                        |    |

|   | 8.3.5 Hold Disable                                                                      |    |

|   | 8.3.6 Error Conditions                                                                  |    |

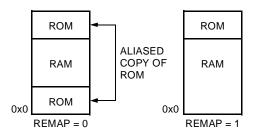

|   | 8.4 ROM/RAM Remapping                                                                   |    |

|   | 8.4.1 Programmable Addresses                                                            |    |

|   | 8.5 EMI FLASH Registers                                                                 |    |

|   | 8.5.1 Chip Select Configuration Register FLASH_CS                                       |    |

|   | 8.5.2 Chip Select Configuration Registers CS1, CS2, CS3                                 |    |

|   | 8.5.3 Hold and Wait-States Encoding                                                     |    |

|   | 8.5.4 Chip Select Base Address Registers FLASH_CS, CS1, CS2, CS3, Internal SRAM         |    |

|   | 8.5.5 Block Size Field Encoding                                                         |    |

|   | 8.5.6 Status Register                                                                   |    |

|   | 8.5.7 Options Register                                                                  |    |

|   | 8.6 External SDRAM Memory Interface                                                     |    |

|   | 8.6.1 External SDRAM Memory Map                                                         |    |

|   | 8.6.2 SDRAM Memory Range Base Address Register                                          |    |

|   |                                                                                         |    |

| tents                                          | Page |

|------------------------------------------------|------|

| 8.6.3 SDRAM Control Register                   |      |

| 8.6.4 SDRAM Timing and Configuration Projector | 00   |

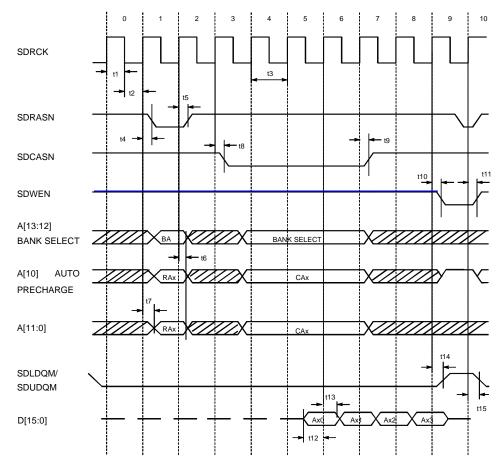

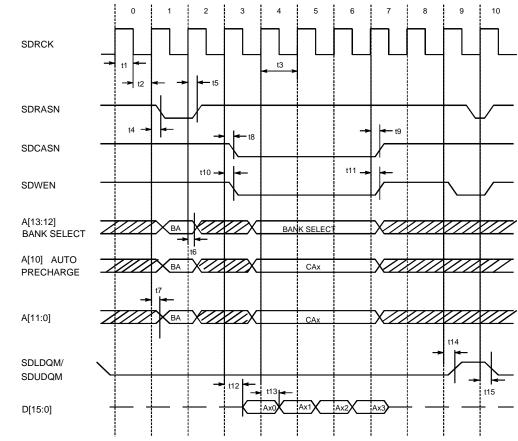

| 8.6.5 SDRAM Manual Access Register       9         8.7 SDRAM Timing       9         8.8 Signals       9         8.8.1 Address, A[23:0]       9         8.8.2 Data, D[15:0]       9         8.8.3 Byte Enable, BETN       9         8.8.4 Read/Write Signals, RDN, WRN       9         8.8.5 Chip Selects, FLASH_CS, CS1, CS2, CS3       9         8.8.5 Chip Selects, FLASH_CS, CS1, CS2, CS3       9         8.8.6 External WAIT, EXWAIT       9         8.8.7 EMI SDRAM, Synchronous DRAM Memory Interface       9         8.8.7 EMI SDRAM, Spnchronous DRAM Memory Interface       9         8.8.8 SDRAM Address Functionality       9         8.8.9 SDRAM Clock, SDRCK       9         8.8.10 SDRASN, SDCASN, SDWEN       9         8.8.11 SDUDQM, SDLDQM       9         9 DSP Communications Controller (DCC)       9         9.1 ARM Processor Memory and I/O Map       99         9.2 DCC Token Register       9         9.3.1 DSP2ARM Interrupt Register       9         9.3.2 ARM 2DSP Interrupt Register       9         9.3.2 ARM 2DSP Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         9       10 </th                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.8 Signals       9         8.8.1 Address, A[23:0]       9         8.8.2 Data, D[15:0]       9         8.8.3 Byte Enable, BE1N       9         8.8.4 Read/Write Signals, RDN, WRN       9         8.8.5 Chip Selects, FLASH_CS, CS1, CS2, CS3       9         8.8.6 External WAIT, EXWAIT       9         8.8.7 EMI SDRAM, Synchronous DRAM Memory Interface       9         8.8.8 SDRAM Address Functionality       9         8.8.10 SDRASN, SDCASN, SDWEN       9         8.8.11 SDUDQM, SDLDQM       9         9 DSP Communications Controller (DCC)       9         9.1 ARM Processor Memory ant I/O Map       9         9.3 DCC Interrupt Register       9         9.3 DCC Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.2 General MAC Information       10         10.2 General MAC Information       10         10.3 MAC Transmitter       10         10.4 Address Matching Registers       10         10.5 MAC Controller, Registers, and Counters       10         10.6 Controller, Registers, and Counters       10         10.7.1 MAC Controller Setup Register            |

| 8.8.1 Address, A[23:0]       9         8.8.2 Data, D[15:0]       9         8.8.2 Data, D[15:0]       9         8.8.3 Byte Enable, BE1N       9         8.8.4 Read/Write Signals, RDN, WRN       9         8.8.5 Chip Selects, FLASH_CS, CS1, CS2, CS3       9         8.8.6 External WAIT, EXWAIT       9         8.8.7 EMI SDRAM, Synchronous DRAM Memory Interface       9         8.8.8 SDRAM Address Functionality       9         8.8.9 SDRAM Clock, SDRCK       9         8.8.10 SDRASN, SDCASN, SDWEN       9         8.8.11 SDUDQM, SDLDQM       9         9 DSP Communications Controller (DCC)       99         9.1 ARM Processor Memory and I/O Map       9         9.2 DCC Token Register       9         9.3 DCC Interrupt Registers       9         9.3.1 DSP2ARM Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.1 Features       10         10.2 General MAC Information       10         10.4.1 Address Matching Registers       10         10.4.1 Address Matching Registers       10         10.5.1 MAC Controller, Registers, and Counters       10                 |

| 8.8.2 Data, D[15:0]       9         8.8.3 Byte Enable, BE1N       9         8.8.4 Read/Write Signals, RDN, WRN       9         8.8.5 Chip Selects, FLASH_CS, CS1, CS2, CS3       9         8.8.6 External WAIT, EXWAIT       9         8.8.7 EMI SDRAM, Synchronous DRAM Memory Interface       9         8.8.7 EMI SDRAM, Synchronous DRAM Memory Interface       9         8.8.8 SDRAM Address Functionality       9         8.8.9 SDRAM Clock, SDRCK       9         8.8.10 SDRASN, SDCASN, SDWEN       9         8.8.11 SDUDQM, SDLDQM       9         9 DSP Communications Controller (DCC)       9         9.1 ARM Processor Memory and I/O Map       9         9.2 DCC Token Register       9         9.3 DCC Interrupt Registers       9         9.3.1 DSP2ARM Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.1 Features       10         10.2 General MAC Information       10         10.4.1 Address Matching Registers       10         10.4.1 Address Matching Registers       10         10.5 MAC Controller, Registers, and Counters       10         10.6 Controller, R |

| 8.8.3 Byte Enable, BE1N       9         8.8.4 Read/Write Signals, RDN, WRN       9         8.8.5 Chip Selects, FLASH_CS, CS1, CS2, CS3       9         8.8.6 External WAIT, EXWAIT       9         8.8.7 EMI SDRAM, Synchronous DRAM Memory Interface       9         8.8.8 SDRAM Address Functionality       9         8.8.9 SDRAM Clock, SDRCK       9         8.8.10 SDRASN, SDCASN, SDWEN       9         8.8.11 SDUDQM, SDLDQM       9         9 DSP Communications Controller (DCC)       9         9.1 ARM Processor Memory and I/O Map       9         9.2 DCC Token Register       9         9.3.1 DSP2ARM Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.1 Features       10         10.2 General MAC Information       10         10.4 MAC Receiver       10         10.5 MAC Controller, Registers, and Counters       10         10.5 MAC Controller, Registers, and Counters       10         10.6 Control Frame Operation       10         10.7 Register Descriptions       10         10.7 Register Descriptions       10                                              |

| 8.8.4 Read/Write Signals, RDN, WRN       9         8.8.5 Chip Selects, FLASH_CS, CS1, CS2, CS3       9         8.8.6 External WAIT, EXWAIT       9         8.8.6 External WAIT, EXWAIT       9         8.8.7 EMI SDRAM, Synchronous DRAM Memory Interface       9         8.8.8 SDRAM Address Functionality       9         8.8.9 SDRAM Clock, SDRCK       9         8.8.10 SDRASN, SDCASN, SDWEN       9         8.8.11 SDUDQM, SDLDQM       9         9 DSP Communications Controller (DCC)       9         9.1 ARM Processor Memory and I/O Map       9         9.2 DCC Token Register       9         9.3 DCC Interrupt Registers       9         9.3.1 DSP2ARM Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.1 Features       10         10.2 General MAC Information       10         10.3 MAC Transmitter       10         10.4 MAC Receiver       10         10.5 MAC Controller, Registers, and Counters       10         10.6 Control Frame Operation       10         10.7 Register Descriptions       10         10.7.1 MAC Controller Setup Register       10 </td       |

| 8.8.5 Chip Selects, FLASH_CS, CS1, CS2, CS3       9         8.8.6 External WAIT, EXWAIT       9         8.8.7 EMI SDRAM, Synchronous DRAM Memory Interface       9         8.8.8 SDRAM Address Functionality       9         8.8.9 SDRAM Clock, SDRCK       9         8.8.10 SDRASN, SDCASN, SDWEN       9         8.8.11 SDUDQM, SDLDQM       9         9 DSP Communications Controller (DCC)       9         9.1 ARM Processor Memory and I/O Map       9         9.2 DCC Token Register       9         9.3 DCC Interrupt Registers       9         9.3.1 DSP2ARM Interrupt Register       9         9.3.1 DSP2ARM Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.1 Features       10         10.2 General MAC Information       10         10.4 MAC Receiver       10         10.5 MAC Controller, Registers, and Counters       10         10.5 MAC Controller, Registers, and Counters       10         10.6 Controller, Registers, and Counters       10         10.6 Controller, Registers       10         10.7 Register Descriptions       10         10.7.1 MAC Controller  |

| 8.8.6 External WAIT, EXWAIT       9         8.8.7 EMI SDRAM, Synchronous DRAM Memory Interface       9         8.8.8 SDRAM Address Functionality       9         8.8.9 SDRAM Clock, SDRCK       9         8.8.10 SDRASN, SDCASN, SDWEN       9         8.8.11 SDUDQM, SDLDQM       9         9 DSP Communications Controller (DCC)       9         9.1 ARM Processor Memory and I/O Map       9         9.2 DCC Token Register       9         9.3.1 DSP2ARM Interrupt Register       9         9.3.2 ARM 2DSP Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.3 MAC Transmitter       10         10.4 MAC Receiver       10         10.5 MAC Controller, Registers, and Counters       10         10.6 Control Frame Operation       10         10.7 Register Descriptions       10         10.7 Register Descriptions       10                                                                                                                                                                                                                                                        |

| 8.8.7 EMI SDRAM, Synchronous DRAM Memory Interface       99         8.8.8 SDRAM Address Functionality       99         8.8.9 SDRAM Clock, SDRCK       99         8.8.10 SDRASN, SDCASN, SDWEN       99         8.8.10 SDRASN, SDLAQM       99         9 DSP Communications Controller (DCC)       99         9.1 ARM Processor Memory and I/O Map       99         9.2 DCC Token Register       99         9.3.1 DSP2ARM Interrupt Register       99         9.3.1 DSP2ARM Interrupt Register       99         9.3.2 ARM 2DSP Interrupt Register       99         9.4 DCC Controller I/O Signals       99         9.5 DSP Read/Write Timing Diagrams       99         10 Ethernet 10/100 MAC       100         10.1 Features       100         10.2 General MAC Information       100         10.3 MAC Transmitter       100         10.4 MAC Receiver       100         10.5 MAC Controller, Registers, and Counters       100         10.6 Control Frame Operation       100         10.6 Control Frame Operation       100         10.7 Register Descriptions       100         10.7.1 MAC Controller Setup Register       10                                                                                        |

| 8.8.8 SDRAM Address Functionality       9         8.8.9 SDRAM Clock, SDRCK       9         8.8.10 SDRASN, SDCASN, SDWEN       9         8.8.11 SDUDQM, SDLDQM       9         9 DSP Communications Controller (DCC)       90         9.1 ARM Processor Memory and I/O Map       90         9.2 DCC Token Register       9         9.3 DCC Interrupt Registers       9         9.3.1 DSP2ARM Interrupt Register       9         9.3.2 ARM 2DSP Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.1 Features       10         10.2 General MAC Information       10         10.3 MAC Transmitter       10         10.4 MAC Receiver       10         10.5 MAC Controller, Registers, and Counters       10         10.5 MAC Controller, Registers, and Counters       10         10.7 Register Descriptions       10         10.7 Register Descriptions       10         10.7.1 MAC Controller Setup Register       10                                                                                                                                                                      |

| 8.8.9 SDRAM Clock, SDRCK       9         8.8.10 SDRASN, SDCASN, SDWEN       9         8.8.11 SDUDQM, SDLDQM       9         9 DSP Communications Controller (DCC)       9         9.1 ARM Processor Memory and I/O Map       9         9.2 DCC Token Register       9         9.3 DCC Interrupt Registers       9         9.3.1 DSP2ARM Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.1 Features       10         10.2 General MAC Information       10         10.4 1 Address Matching Registers       10         10.5 MAC Controller, Registers, and Counters       10         10.5 MAC Controller, Registers, and Counters       10         10.7 Register Descriptions       10         10.7 Register Descriptions       10         10.7 MAC Controller Setup Register       10                                                                                                                                                                                                                                                                                                    |

| 8.8.10 SDRASN, SDCASN, SDWEN       9         8.8.11 SDUDQM, SDLDQM       9         9 DSP Communications Controller (DCC)       9         9.1 ARM Processor Memory and I/O Map       9         9.2 DCC Token Register       9         9.3 DCC Interrupt Registers       9         9.3.1 DSP2ARM Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.2 General MAC Information       10         10.3 MAC Transmitter       10         10.4.1 Address Matching Registers       10         10.5 MAC Controller, Registers, and Counters       10         10.7 Register Descriptions       10         10.7 Register Descriptions       10         10.7.1 MAC Controller Setup Register       10                                                                                                                                                                                                                                                                                                                                               |

| 8.8.11 SDUDQM, SDLDQM       9         9 DSP Communications Controller (DCC)       9         9.1 ARM Processor Memory and I/O Map       9         9.2 DCC Token Register       9         9.3 DCC Interrupt Registers       9         9.3.1 DSP2ARM Interrupt Register       9         9.3.2 ARM 2DSP Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.1 Features       10         10.2 General MAC Information       10         10.3 MAC Transmitter       10         10.4 1 Address Matching Registers       10         10.5 MAC Controller, Registers, and Counters       10         10.6 Control Frame Operation       10         10.7 Register Descriptions       10         10.7.1 MAC Controller Setup Register       10                                                                                                                                                                                                                                                                                                                                                            |

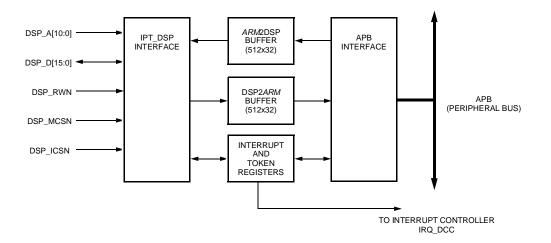

| 9 DSP Communications Controller (DCC)       9         9.1 ARM Processor Memory and I/O Map       9         9.2 DCC Token Register       9         9.3 DCC Interrupt Registers       9         9.3.1 DSP2ARM Interrupt Register       9         9.3.2 ARM 2DSP Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.1 Features       10         10.2 General MAC Information       10         10.3 MAC Transmitter       10         10.4.1 Address Matching Registers       10         10.5 MAC Controller, Registers, and Counters       10         10.6 Control Frame Operation       10         10.7 Register Descriptions       10         10.7.1 MAC Controller Setup Register       10                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9.1 ARM Processor Memory and I/O Map99.2 DCC Token Register99.3 DCC Interrupt Registers99.3.1 DSP2ARM Interrupt Register99.3.2 ARM 2DSP Interrupt Register99.4 DCC Controller I/O Signals99.5 DSP Read/Write Timing Diagrams910 Ethernet 10/100 MAC1010.1 Features1010.2 General MAC Information1010.3 MAC Transmitter1010.4 MAC Receiver1010.5 MAC Controller, Registers, and Counters1010.6 Control Frame Operation1010.7 Register Descriptions1010.7.1 MAC Controller Setup Register10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9.2 DCC Token Register       9         9.3 DCC Interrupt Registers       9         9.3.1 DSP2ARM Interrupt Register       9         9.3.2 ARM 2DSP Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.1 Features       10         10.2 General MAC Information       10         10.3 MAC Transmitter       10         10.4.1 Address Matching Registers       10         10.5 MAC Controller, Registers, and Counters       10         10.6 Control Frame Operation       10         10.7 Register Descriptions       10         10.7.1 MAC Controller Setup Register       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 9.3 DCC Interrupt Registers       9         9.3.1 DSP2ARM Interrupt Register       9         9.3.2 ARM 2DSP Interrupt Register       9         9.4 DCC Controller I/O Signals       9         9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.1 Features       10         10.2 General MAC Information       10         10.3 MAC Transmitter       10         10.4 MAC Receiver       10         10.5 MAC Controller, Registers, and Counters       10         10.6 Control Frame Operation       10         10.7 Register Descriptions       10         10.7.1 MAC Controller Setup Register       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 9.3.1 DSP2ARM Interrupt Register       99         9.3.2 ARM 2DSP Interrupt Register       99         9.4 DCC Controller I/O Signals       99         9.5 DSP Read/Write Timing Diagrams       99         10 Ethernet 10/100 MAC       100         10.1 Features       100         10.2 General MAC Information       100         10.3 MAC Transmitter       100         10.4 MAC Receiver       100         10.5 MAC Controller, Registers, and Counters       100         10.6 Control Frame Operation       100         10.7 Register Descriptions       100         10.7.1 MAC Controller Setup Register       100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

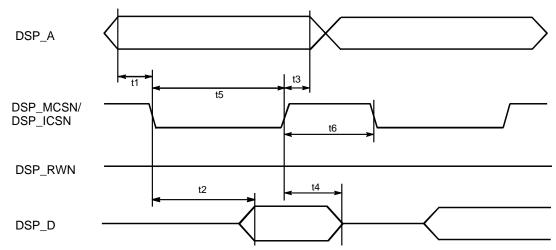

| 9.3.2 ARM 2DSP Interrupt Register       9.4         9.4 DCC Controller I/O Signals       99.9         9.5 DSP Read/Write Timing Diagrams       99.10         10 Ethernet 10/100 MAC       100         10.1 Features       100         10.2 General MAC Information       100         10.3 MAC Transmitter       100         10.4 MAC Receiver       100         10.5 MAC Controller, Registers, and Counters       100         10.6 Control Frame Operation       100         10.7 Register Descriptions       100         10.7.1 MAC Controller Setup Register       100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9.4 DCC Controller I/O Signals99.5 DSP Read/Write Timing Diagrams910 Ethernet 10/100 MAC1010.1 Features1010.2 General MAC Information1010.3 MAC Transmitter1010.4 MAC Receiver1010.4.1 Address Matching Registers1010.5 MAC Controller, Registers, and Counters1010.6 Control Frame Operation1010.7 Register Descriptions1010.7.1 MAC Controller Setup Register10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

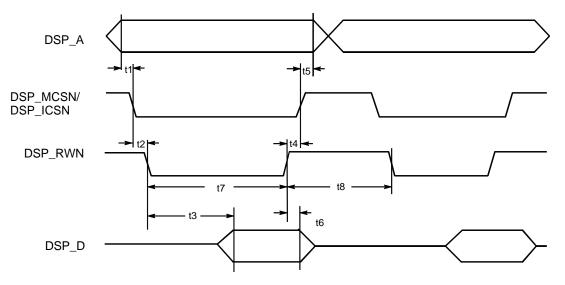

| 9.5 DSP Read/Write Timing Diagrams       9         10 Ethernet 10/100 MAC       10         10.1 Features       10         10.2 General MAC Information       10         10.3 MAC Transmitter       10         10.4 MAC Receiver       10         10.4.1 Address Matching Registers       10         10.5 MAC Controller, Registers, and Counters       10         10.6 Control Frame Operation       10         10.7 Register Descriptions       10         10.7.1 MAC Controller Setup Register       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

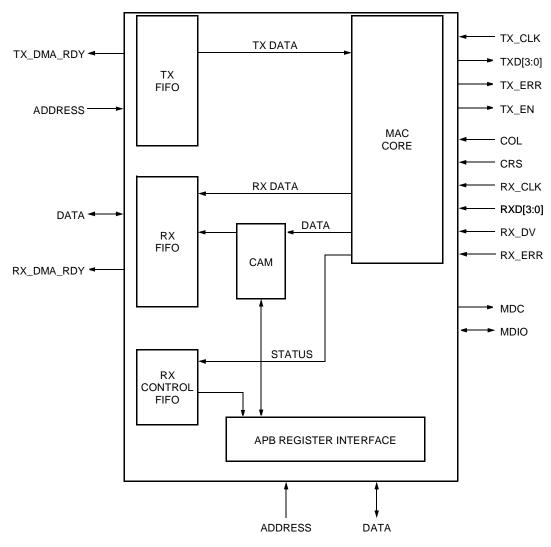

| 10       Ethernet 10/100 MAC       10         10.1       Features       10         10.2       General MAC Information       10         10.3       MAC Transmitter       10         10.4       MAC Receiver       10         10.4.1       Address Matching Registers       10         10.5       MAC Controller, Registers, and Counters       10         10.6       Control Frame Operation       10         10.7       Register Descriptions       10         10.7.1       MAC Controller Setup Register       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10.1 Features       10.         10.2 General MAC Information       10.         10.3 MAC Transmitter       10.         10.4 MAC Receiver       10.         10.4.1 Address Matching Registers       10.         10.5 MAC Controller, Registers, and Counters       10.         10.6 Control Frame Operation       10.         10.7 Register Descriptions       10.         10.7.1 MAC Controller Setup Register       10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10.2 General MAC Information       10.         10.3 MAC Transmitter       10.         10.4 MAC Receiver       10.         10.4.1 Address Matching Registers       10.         10.5 MAC Controller, Registers, and Counters       10.         10.6 Control Frame Operation       10.         10.7 Register Descriptions       10.         10.7.1 MAC Controller Setup Register       10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10.3 MAC Transmitter       10.         10.4 MAC Receiver       10.         10.4.1 Address Matching Registers       10.         10.5 MAC Controller, Registers, and Counters       10.         10.6 Control Frame Operation       10.         10.7 Register Descriptions       10.         10.7.1 MAC Controller Setup Register       10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10.4 MAC Receiver       10.         10.4.1 Address Matching Registers       10.         10.5 MAC Controller, Registers, and Counters       10.         10.6 Control Frame Operation       10.         10.7 Register Descriptions       10.         10.7.1 MAC Controller Setup Register       10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10.4.1 Address Matching Registers       10.         10.5 MAC Controller, Registers, and Counters       10.         10.6 Control Frame Operation       10.         10.7 Register Descriptions       10.         10.7.1 MAC Controller Setup Register       10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 10.5 MAC Controller, Registers, and Counters       10.         10.6 Control Frame Operation       10.         10.7 Register Descriptions       10.         10.7.1 MAC Controller Setup Register       10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10.6 Control Frame Operation       10         10.7 Register Descriptions       10         10.7.1 MAC Controller Setup Register       10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10.7 Register Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.7.1 MAC Controller Setup Register10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10.7.2 MAC Packet Delay Alarm Value Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10.7.3 MAC Controller Interrupt Enable Register10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10.7.4 MAC Control Frame Destination Address Registers10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10.7.5 MAC Control Frame Source Address Registers10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10.7.6 MAC Control Frame Length/Type Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10.7.7 MAC Control Frame Opcode Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.7.8 MAC Control Frame Data Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10.7.9 VLAN Type1 Type/Length Field Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10.7.10 VLAN Type2 Type/Length Field Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10.7.11 MAC Transmit FIFO Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10.7.12 MAC Receive FIFO Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10.7.13 MAC Receive Control FIFO Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10.7.14 MDIO Address Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10.7.15 MDIO Data Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10.7.16 MAC PHY Powerdown Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10.7.17 MAC Controller Transmit Control Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# Contents

|     | 10.7.19 MAC Controller Transmit Start Degister                      | 110   |

|-----|---------------------------------------------------------------------|-------|

|     | 10.7.18 MAC Controller Transmit Start Register                      |       |

|     | 10.7.19 MAC Transmit Status Register                                |       |

|     | 10.7.20 MAC Collision Counter                                       |       |

|     | 10.7.21 MAC Packet Delay Counter                                    |       |

|     | 10.7.22 MAC Transmitted Packet Counter                              |       |

|     | 10.7.23 MAC Transmitted Single Collision Counter                    |       |

|     | 10.7.24 MAC Transmitted Multiple Collision Counter                  |       |

|     | 10.7.25 MAC Excess Collision Counter                                |       |

|     | 10.7.26 MAC Packet Deferred Counter                                 |       |

|     | 10.7.27 MAC Controller Receive Control Register                     |       |

|     | 10.7.28 MAC FIFO Status Register                                    |       |

|     | 10.7.29 MAC Controller Interrupt Status Register                    |       |

|     | 10.8 Signal Information                                             |       |

|     | 10.8.1 MII MAC I/O Signals                                          |       |

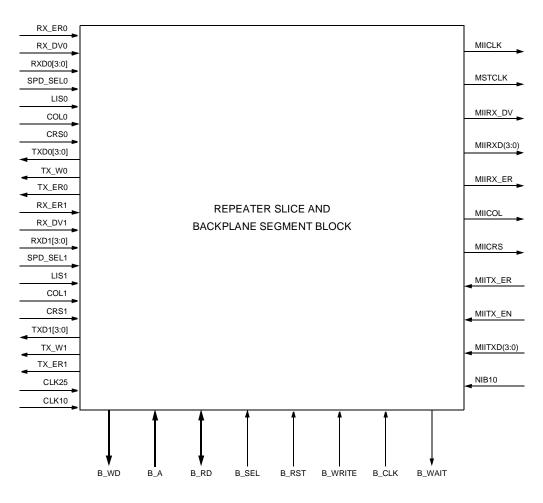

| 11  | 10/100 2-Port Repeater and Backplane Segment Controller             |       |

|     | 11.1 MII Transmit and Receive Interface                             |       |

|     | 11.1.1 Repeater Slice Interface                                     |       |

|     | 11.1.2 PHY Interface                                                | 124   |

|     | 11.1.3 Backplane Interface                                          | 125   |

|     | 11.1.3.1 MAC Interface                                              | 125   |

|     | 11.1.4 Receive Path                                                 | 126   |

|     | 11.1.5 Transmit Path                                                | 126   |

|     | 11.2 Input Clocks                                                   | 126   |

|     | 11.3 Repeater Slice Theory of Operation                             | 126   |

|     | 11.3.1 Repeater Core                                                | 126   |

|     | 11.3.2 10/100 Mbits/s Operation                                     |       |

|     | 11.3.3 Collisions                                                   | 127   |

|     | 11.3.4 Partition and Isolate                                        | 127   |

|     | 11.3.4.1 Partitioning                                               | 127   |

|     | 11.3.4.2 MAU Jabber Lockup Protection (MJLP)                        |       |

|     | 11.3.4.3 Receive Jabber                                             |       |

|     | 11.3.4.4 Isolate on an Incorrect Clock Frequency                    |       |

|     | 11.3.4.5 Automatic Speed Mismatch Protection                        |       |

|     | 11.3.5 Carrier Integrity Monitor                                    |       |

|     | 11.4 Repeater Slice Interfaces                                      |       |

|     | 11.4.1 Repeater Slice ARM Interface                                 |       |

|     | 11.4.2 Repeater Slice Interface                                     |       |

|     | 11.4.3 Repeater Slice Input Clocks                                  |       |

|     | 11.4.4 Backplane Segment 10/100 Mbits/s Serial Mac Interface Port B |       |

|     | 11.5 Repeater Slice Register Map                                    |       |

|     | 11.5.1 Global Maximum Frame Size Register                           |       |

|     | 11.5.2 Global Configuration Register                                |       |

|     | 11.5.3 Port Control Registers, for Port 0, 1                        |       |

|     | 11.5.4 Port Configuration Register 0 for Port 0, 1                  |       |

|     | 11.5.5 Port Configuration Register 1, for Port 0, 1                 |       |

|     | 11.5.6 Global Interrupt Enable Register                             |       |

|     | 11.5.7 Global Interrupt Status Register                             |       |

|     | 11.5.8 Global Port Status Register, for Port 0, 1                   |       |

| 12  | Ethernet 10/100 PHY(s)                                              |       |

| . ~ | 12.1 10 Mbits Transceiver Features                                  |       |

|     |                                                                     | · · ć |

# Contents

|    | 12.2 100 Mbits/s Transceiver Features                                                     | 142 |

|----|-------------------------------------------------------------------------------------------|-----|

|    | 12.3 General Features                                                                     |     |